VeriRAG: A Knowledge Graph-Augmented RAG for Verilog and Assertion Generation

VeriRAG is an open-source framework that unifies Knowledge Graphs (KG) and Retrieval-Augmented Generation (RAG) for intelligent Verilog automation. It enables semantic understanding, retrieval, and generation of Register Transfer Level (RTL) and System Verilog Assertions (SVA) code using Large Language Models (LLMs), RDF (Resource Description Framework) graphs, and vector databases. Experimental results across a diverse set of representative designs show that VeriRAG achieves up to 97% syntax correctness and 100% functional success for RTL generation, with SVAs reaching 100% syntax validity and 95% Formal Property Verification (FPV) pass rates using standard EDA tools.

The paper will be presented at ASP-DAC, 2026 and the framework can be found here .

VeriRAG Flow

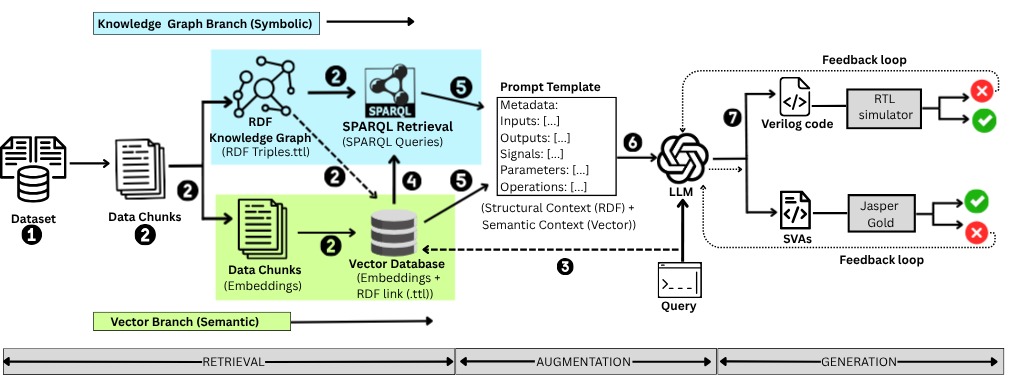

A curated RTL dataset is split into chunks and processed via a knowledge graph branch (RDF triples) and a vector branch (embeddings). At inference, a user query triggers hybrid retrieval (vector + SPARQL), merging results into a prompt template for the LLM to generate synthesizable Verilog modules and SVAs, which are automatically verified for syntax and functional correctness, with failed outputs iteratively refined.

How does VeriRAG differ from conventional RAG frameworks?

Unlike standard RAG systems that rely solely on text retrieval, VeriRAG integrates symbolic reasoning and semantic search. It uses RDF Knowledge Graphs for structural relationships and vector-based retrieval for contextual similarity, enabling both accurate and meaningful Verilog synthesis

How does hybrid retrieval work?

VeriRAG performs both SPARQL-based logical retrieval on the RDF graph and semantic retrieval on the vector database. The results from both systems are merged to create a context-rich prompt for LLMs, ensuring that the generated Verilog is both logically consistent and semantically relevant.

What inputs does VeriRAG require?

VeriRAG accepts Verilog RTL files (.v) or structured CSV metadata describing module-level information such as ports, signals, and parameters.

How are generated results verified?

VeriRAG evaluates the generated designs through simulation-based and formal verification methods. These can be connected to tools like Icarus Verilog, Xcelium, VCS or JasperGold to validate the generated RTL or SVA outputs.