# Synplify

- A synthesis tool from Synplicity

- Interprets high-level HDL description

- Converts HDL into small, highperformance, design netlists optimized for popular FPGAs

ECE 297 - Reconfigurable Architectures for Computer Security

- Writes results to standard EDIF file

- Can write post-synthesis VHDL or Verilog netlists for simulation

- Synthesizable subset of VHDL93 and following packages

- std\_logic\_1164

- numeric\_std

- numeric\_bit

- std\_logic\_unsigned

- std\_logic\_signedstd\_logic\_arith

- Synthesizable subset of Verilog95

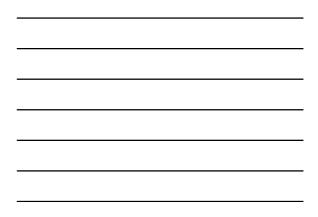

# Starting New Project (2)

- Next add all other library files that are not built into Synplify

- Add your files at the end

- Order of files in the project matters and should reflect hierarchy of the design

| Starting New                                                             | v Project (5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <ul> <li>Choose top level<br/>entity and encodir<br/>for FSMs</li> </ul> | 1 <b>g</b><br>Protect Wirord - Hild Dobions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ×          |

|                                                                          | Select the top level entity for the design. (optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | s aplicity |

|                                                                          | Top Level Entry:<br>multipled<br>Dataut Exam Encoding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|                                                                          | Concernent and the second of t |            |

|                                                                          | CBack Next> Finish Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Help       |

| er Chodowiec ECE 297 - Recor                                             | figurable Architectures for Computer Security                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

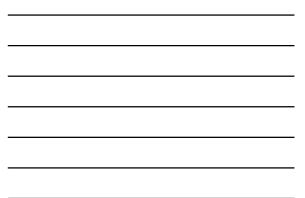

# **Fanout Guide**

- Sets the maximum limit for number of inputs driven by one output

- Not a hard limit. To set a hard limit use syn\_maxfan attribute

- Large fanouts can cause large delays and routability problems

- Low fanouts result in excessive logic replication and buffering

ECE 297 - Reconfigurable Architectures for Computer Security

# Disable I/O insertion

- Useful when the synthesized circuit will later be instantiated in another circuit

- If you try to implement the circuit with disabled I/O the mapper will optimize all the logic away

ECE 297 - Reconfigurable Architectures for Computer Security

12

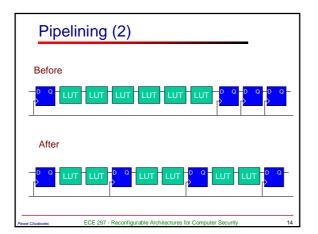

# Pipelining (1)

- Automatically pipelines multipliers and ROMs

- Pipeline registers must exist in the RTL code and will be pushed into the module that needs to be pipelined

ECE 297 - Reconfigurable Architectures for Computer Security

13

15

- Registers must have the same clock, set/reset (or none) and enable

- ROMs must be at least 512 words

## Modular Design

• Support for large designs developed in modules by different groups of people

### Retiming

- Moves registers (register balancing) across combinational gates or LUTs ensuring identical behavior

- Does not change the number of registers in the path but may change total number of registers in the design

ECE 297 - Reconfigurable Architectures for Computer Security

16

Is a superset of Pipelining

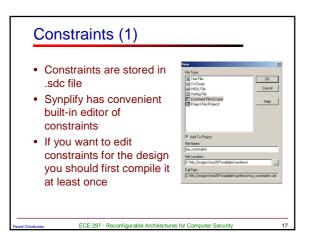

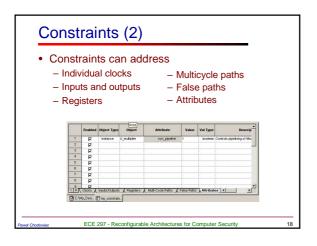

### Attributes

- Attributes can be edited either in constraints editor or added in VHDL code

- For the list of allowed attributes refer to Synplify PRO Reference Manual

ECE 297 - Reconfigurable Architectures for Computer Security

19

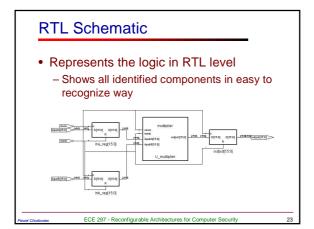

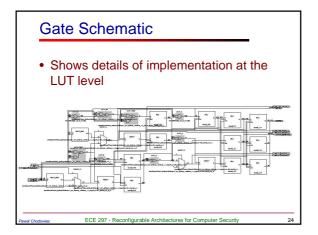

### **Synthesis**

- After all options and constraints are set simply push the RUN button

- Results of synthesis are available to view in the form of schematics (RTL and Gate Netlists) and report file .srr

- Simulation netlists are created only when appropriate implementation options are checked

- · EDIF file is generated automatically

ECE 297 - Reconfigurable Architectures for Computer Security

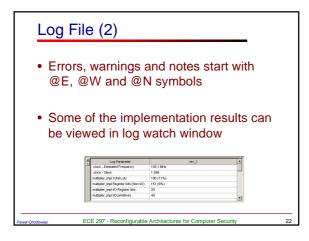

# Log File (1)

- To view log file push www.button

- Log file contains detailed information about your implementation

- errors, warnings and notes

- estimated performance

- critical path(s)

- circuit size

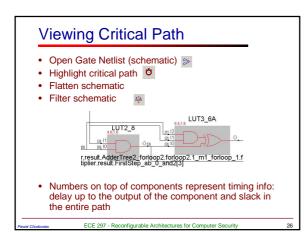

## **Viewing Schematics**

- Operations allowed on schematics

- Moving across hierarchy

- Zooming

- Flattening

- Filtering to selected components

- Viewing critical path

ECE 297 - Reconfigurable Architectures for Computer Security

# **Tips and Tricks**

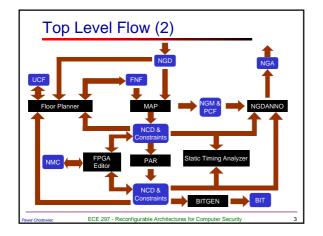

- NGDBulid

- If some constraints cannot be forward annotated by Synplify add them in UCF file

- MAP

- Do not map to 5-input functions. Do not use -k option at all.

- PAR

- Do not use effort level of 5. Set it to 4 at most using -l4 option